# Design and Simulation MOSFET Models: Closing the Gap

Paul Jespers and Andrei Vladimirescu Université Catholique de Louvain UC Berkeley/BWRC and ISEP

#### **Motivation**

- > Develop a MOSFET model for analog design

- Must describe all regions of operation

- Simulation models have become

- Very accurate, but...

- Very complex, inadequate for hand calculation!

- Design is not done "by SPICE"!

- Model used in design must be simple but relatively accurate

- SPICE provides the ultimate accurate verification

- Start from physics

- Minimize number of parameters

- Use Matlab for help!

#### **Overview**

- Applications and Requirements

- Compact Model Approximation

- Basic Equations

- Parameters and their Extraction

- g<sub>m</sub>/I<sub>D</sub> Analog Design Methodology

- Design Example

- Opamp Design

- Design Verification

- Conclusion

P. Jespers, A. Vladimirescu

ESSCIRC'06

3

#### **Applications of Device Models**

- ▶ Estimation/Design

- > Simple for hand-calculation

- Accurate for relevant results!

- > Examples: Level=1, α-Power

- Circuit Simulation (SPICE)

- Currents and Charges function of terminal voltages

- Continuous functions and first derivatives over

- All regions of operations

- Temperatures

- Geometries

- Model parameters: physical and scalable

- Device Simulation

- Semiconductor-device physics carrier concentrations

P. Jespers, A. Vladimirescu

ESSCIRC'06

Δ

## **Device Model Requirements** for IC Design Applications

- Digital Circuits

- Very accurate I<sub>ON</sub> and I<sub>OFF</sub> (subthreshold)

- > No negative conductances

- Analog Circuits

- > Accurate everywhere especially transition regions!

- Accurate I<sub>D</sub> in all regions

- Accurate values for small-signal

- g<sub>m</sub>, g<sub>ds</sub>, g<sub>mbs</sub>, Cgs, Cgd

- Correct small-size

P. Jespers, A. Vladimirescu

ESSCIRC'06

5

#### **Application: Analog CMOS Design**

- $\rightarrow$  Operation at low  $V_{GS}$ - $V_{TH}$  (Moderate Inversion)

- Maximum gain according to LEVEL=1 (strong-inversion only)

$$a_{v} = \frac{g_{m}}{g_{o}} = \frac{2}{\lambda (V_{GS} - V_{TH})}$$

- $V_{GS}$   $V_{TH} \downarrow a_v \uparrow$ ;  $V_{GS}$   $V_{TH} \rightarrow 0$ ,  $a_v \rightarrow \infty$ , better model is needed!

- Low-power moderate or weak inversion

- Operation up to the edge of saturation

- Max output resistance

- Max output swing

- Estimation model accuracy needed

- from weak to strong inversion

- > Big Gap with latest simulation models!

#### **Overview**

- Applications and Requirements

- Compact Model Approximation

- Basic Equations

- Parameters and their Extraction

- g<sub>m</sub>/I<sub>D</sub> Analog Design Methodology

- Design Example

- Opamp Design

- Design Verification

- Conclusion

P. Jespers, A. Vladimirescu

ESSCIRC'06

7

#### **Charge-Based Estimation Model**

Charge Sheet Model (surface potential model)

$$I_D dx = \mu W \left[ -Q_i' d\psi_S + U_T dQ_i' \right]$$

- Compact Model replace  $\psi_s$  by mobile charge density  $Q_i^{\prime}$

- by introducing constant parameter n (the slope factor)

$$d\left(-\frac{Q_i'}{C_{oc}'}\right) = -\underline{n}d\psi_S$$

$$I_D dx = -\mu C'_{ox} W \left[ \frac{1}{n} \left( -\frac{Q'_i}{C'_{ox}} \right) + U_T \right] d \left( -\frac{Q'_i}{C'_{ox}} \right)$$

- A charge sheet model for the MOSFET. Solid-State-Electronics. Vol. 21, p 345-355, 1978.

- [2] Cunha A.I.A., Scheider M.C. and Galup-Montoro C. And Calup-Montoro C. An MOS transistor mode for analog circuit design. IEEE. JSCC, vol 33, n° 10, p 1510-1519, oct 1998,

[3] Enc C., Krummenacher F. and Vittoz E. An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications. Analog Integrated Circuits and Signal Processing, Vol 8, p 83-114, 1995.

- P. Jespers, A. Vladimirescu

## **Charge-Based Estimation Model (Cont'd)**

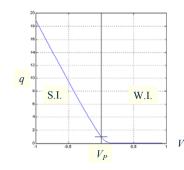

> Define normalized q,

$$q = -\frac{Q_i'}{2nU_T C_{ox}'}$$

> Define the specific current  $I_S$ , the transition point W.I. – S.I.

$$I_{S} = 2nU_{T}^{2}\mu C_{ox}' \frac{W}{L} = 2nU_{T}^{2}\beta$$

Normalized current – charge equation

$$i = \frac{I_D}{I_S} = [q^2 + q]_{V_D}^{V_S} = i_F - i_R$$

- ightharpoonup Forward normalized current  $i_F=q_S^2+q_S$

- » Reverse normalized current  $i_R = q_D^2 + q_D$

- P. Jespers, A. Vladimirescu

ESSCIRC'06

9

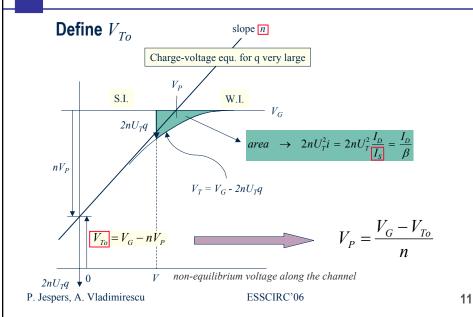

### **Drain, Source Voltage**

- Charge-voltage equation

- **⇒** (SEMI-COND PHYSICS + CONSTANT *n* APPROX)

$$V_P - V = U_T [2(q-1) + \log(q)]$$

$V_P$  pinch-off voltage (q=1) V is the non-equilibrium voltage along the channel  $V=V_S$  at the source  $V=V_D$  at the drain

P. Jespers, A. Vladimirescu

ESSCIRC'06

#### **Gate Voltage**

## $I_D - V_G$ Characteristic – General Philosophy

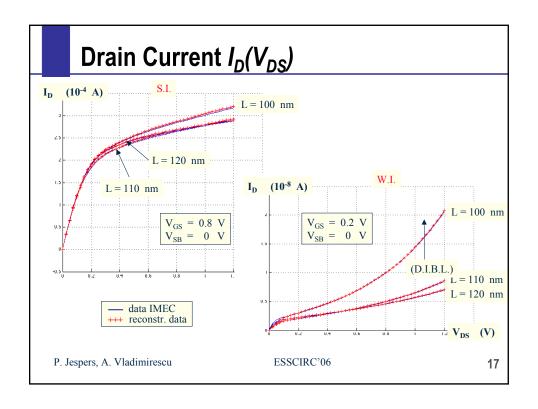

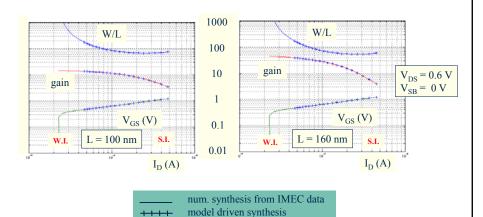

- The shape of the  $I_D(V_G)$  characteristic changes little as the channel length shrinks, displaying weak (W.I.) and strong inversion (S.I.) regions separated by a moderate inversion region (M.I.).

- The gate controls the inversion layer especially, whereas source and drain control not only the inversion layer but also the regions below and near the junctions.

- Compact models derived from the Charge Sheet representation lend themselves to better representations for gate-driven configurations than source- and/or drain-driven.

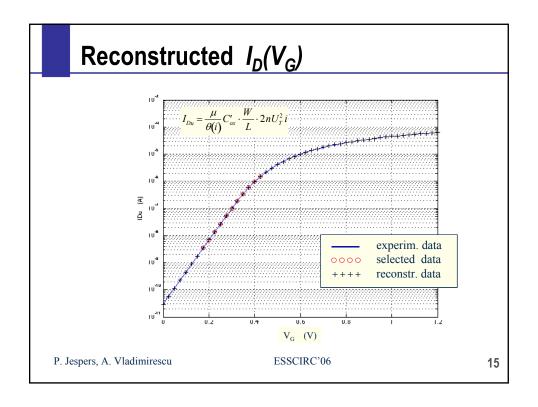

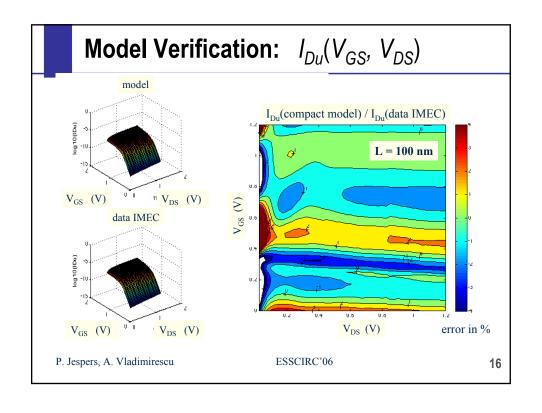

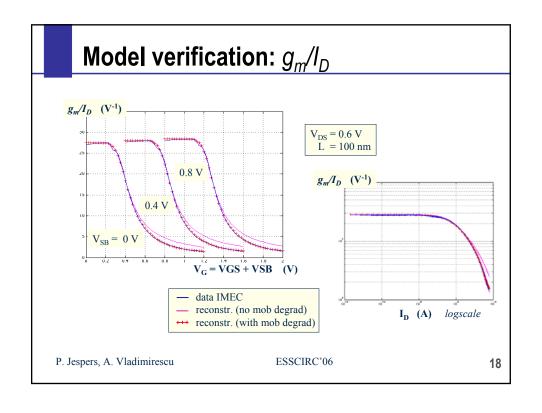

- It is possible to reconstruct  $I_D(V_{GS})$  characteristics with less than 2 to 3 % error with only three parameters n,  $I_S$  and  $V_{TO}$  and a small-size polynomial  $\Theta(i)$  rendering mobility degradation.

n,  $I_{\rm s}$ ,  $V_{\rm To}$  and the coeffs of  $\theta$  poly depend on  $V_{\rm DS}$ ,  $V_{\rm SB}$  and L, not on  $V_{\rm GS}$ .

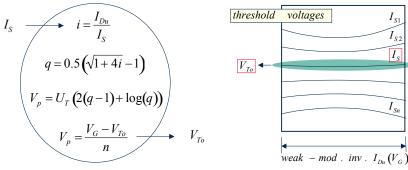

#### Model Parameters n, $V_{To}$ , $I_S$ and $\theta$ poly given $V_{DS}$ , $V_{BS}$ and La) 000 select data in weak-mod inv W.I. approx. b) extract param. $n, V_{T0}, I_S$ c) +++ reconstruct $I_{Du}(V_G)$ $k \le 2 \text{ to } 3$ d) find coeff. of fitting polynomial $theta(i(V_G))$ 10-8 experim. data ++ reconstr. over exper. data 3d order polynomial fit $theta(i(V_G))$ selected data 10° reconstr. data max slope $V_{G}$ (V) 1.2 V low-power 90 nm technology (by courtesy of IMEC)

## Parameter Extraction: n, $V_{To}$ and $I_{S}$

ESSCIRC'06

- 1) choose  $I_{Du}(V_G)$  in weak and moderate inversion

- 2) n max. of subthreshold slope

- 3) Iteratively find  $I_S$  that minimizes variance of  $V_{To}$  for selected  $I_{Du}$ 's ( $I_D$  for W = 1  $\mu$ m)

P. Jespers, A. Vladimirescu

P. Jespers, A. Vladimirescu

ESSCIRC'06

14

#### **Overview**

- Applications and Requirements

- Compact Model Approximation

- Basic Equations

- Parameters and their Extraction

- ▶ g<sub>m</sub>/I<sub>D</sub> Analog Design Methodology

- > Design Example

- Opamp Design

- Design Verification

- Conclusion

P. Jespers, A. Vladimirescu

ESSCIRC'06

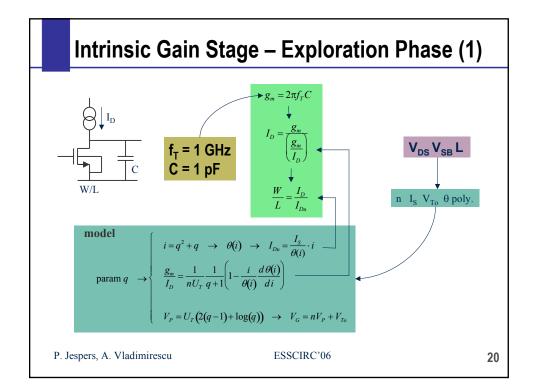

#### **Intrinsic Gain Stage – Exploration Phase (2)**

P. Jespers, A. Vladimirescu

ESSCIRC'06

21

#### **Design methodology**

- g<sub>m</sub>/I<sub>D</sub> methodology\* is used to derive sizing and currents of the desired circuit

- $g_m/I_D = f(I_D/(W/L))$

- $\triangleright$  Relates  $g_m$ , power, MOS geometry

- Set source and drain voltages

Fixes  $n I_s$  etc..

Allows the evaluation of  $g_m/I_D$  versus  $V_G$

- > Choose current levels as independent variables

- Derive I<sub>D</sub> and W/L of MOSFET

<sup>\*</sup> F. Silveira, D. Flandre, and P. G. A. Jespers, "A  $g_{m}/l_{D}$  Based Methodology for the Design of CMOS Analog Circuits and Its Application to the Synthesis of a SOI Micropower OTA" IEEE JSSC, vol. 31, pp. 1314 -1319, Sept. 1996.

#### **Design Flow**\*

#### Exploration phase (Matlab)

- Capture circuit performance in analytical expressions

- Apply proposed MOSFET estimation model with parameters n, Is, V<sub>To</sub> extracted for target technology

- Plot multi-parametric design space

#### Design phase (Constrained optimization in Matlab)

- Use Matlab Optimization Toolbox to improve performance in selected design point

- Selected objective function is optimized

- under performance and bias constraints

#### Verification and Process centering phase (SPICE)

- Uses foundry provided process data with simulation MOSFET model

- Applies optimization for improving objective performance under constraints

#### Automated layout from sized schematic

\* A. Vladimirescu, R. Zlatanovici and P. G. A. Jespers, "Analog Circuit Synthesis using Standard EDA Tools", Proc. Int. Symposium on Circuit and Systems, May 2006.

P. Jespers, A. Vladimirescu

ESSCIRC'06

23

#### **Overview**

- > Applications and Requirements

- Compact Model Approximation

- Basic Equations

- Parameters and their Extraction

- ▶ g<sub>m</sub>/I<sub>D</sub> Analog Design Methodology

- Design Example

- Opamp Design

- Design Verification

- Conclusion

P. Jespers, A. Vladimirescu

ESSCIRC'06

#### Design example: CMOS Miller opamp

- $M_{1a,b}$  are sized based on the desired bandwidth  $\omega_{\tau}$ :  $g_{m1} = \omega_T \cdot C_m$

- Non-dominant pole  $\omega_{NDP}$  and the zero  $\omega_{Z}$  -> phase  $\omega_{NDP} = NDP \cdot \omega_T; \quad \omega_Z = Z \cdot \omega_T$

- ${\rm M_{3a,b}}$  have the same gate voltage as  ${\rm M_2}$  for minimizing offset;

- $\rm M_{\rm p},\,M_{\rm 4}$  and  $\rm M_{\rm 5}$  operate in strong inversion and are sized to provide the desired current levels in the differential pair and second stage;

- The W/L of the transistors can be computed

- Inversion level  $i_1$  for transistors  $M_{1a,b}$ , and  $i_2$ , for M2, are taken as parameters

- in the design space of equal area, gain and currentsupply curves

- Transistors' L vs. L<sub>min</sub>

- $L_{M1} = 3* L_{min}; L_{M3} = 7* L_{min}; L_{M2} = L_{min}; L_{M4} = 3* L_{min}; L_{M5,Mb} = 10* L_{min}$  $(W/L)_3 = I_{D1}/I_{D2} \cdot (W/L)_3$

$\frac{W}{L} = \frac{I_D}{2 \cdot n \cdot V_{th}^2 \cdot \mu \cdot C_{td}}$

Symmetry and Matching

$(W/L)_4 = I_{D2}/2I_{D1} \cdot (W/L)_5$

P. Jespers, A. Vladimirescu

ESSCIRC'06

25

(3)

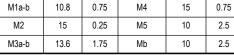

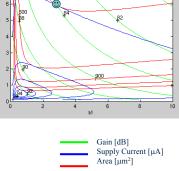

## **Exploration phase**

- Performance space and initial sizing

- Design tradeoffs between Gain, Supply current and Area

- Select:

- Figure 3. Gain (GBW as  $\omega_{\tau}$  is set) = 84 dB

- Supply current = 53 μA

- i<sub>1</sub>=2.9, i<sub>2</sub>=6 in a 0.25μm technology

- Resulting W and L's for this design point

- > Lead to min Area of 300  $\mu m^2$

- Did not take into account terminal voltages! Initial sizes:

| Transistor | W (µm) | L (µm) | Transistor | W (µm) | L (µm) |

|------------|--------|--------|------------|--------|--------|

| M1a-b      | 10.8   | 0.75   | M4         | 15     | 0.75   |

| M2         | 15     | 0.25   | M5         | 10     | 2.5    |

| M3a-b      | 13.6   | 1.75   | Mb         | 10     | 2.5    |

P. Jespers, A. Vladimirescu

### **Design phase**

- Constrained design optimization

- Maximize GBW

- Parameters: I<sub>D1</sub>, I<sub>D2</sub>, (W/L)<sub>1</sub>, (W/L)<sub>2</sub>, (W/L)<sub>3</sub>

- Constraints: DC, AC, transient, symmetry

$$V_{GT} = 2nU_T \log \left[ \exp \left( \sqrt{\frac{I_D}{2nU_T^2 K_{n/p}(W/L)}} \right) - 1 \right]$$

| Zero              | $\omega_{Z} \geq Z \cdot \omega_{T}$                  |  |  |

|-------------------|-------------------------------------------------------|--|--|

| Non-dominant pole | $\omega_{NDP} \geq NDP \cdot \omega_{T}$              |  |  |

| Slew rate         | $2 \cdot I_{D1} / C_m \ge SR_{min}$                   |  |  |

| Unity gain bw     | $\omega_{T} \geq \omega_{min}$                        |  |  |

| M5 bias           | $V_{GT5} + V_{GT1} \le V_{DD} - V_{cm,max} - V_{T,p}$ |  |  |

| M4 bias           | $V_{GT4} \le V_{DD} - V_{out,max}$                    |  |  |

| M2 bias           | $V_{GT2} \le V_{out,,min}$                            |  |  |

| M1 bias           | $V_{GT1} \le V_{cm,min} + V_{T,p} - V_{T,n}$          |  |  |

P. Jespers, A. Vladimirescu

ESSCIRC'06

27

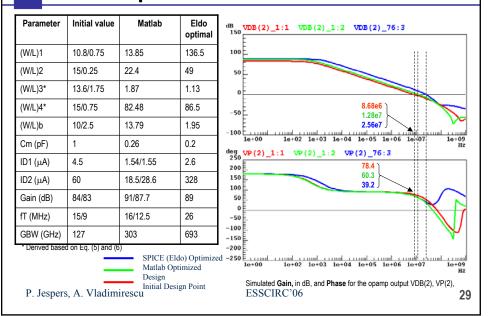

#### Verification phase

- > SPICE verification with actual process parameters

- Design objective:

- Maximize Gain: 84 dB min

- Main constraints

- > Unity-gain Bandwidth ≥ 10 MHz

- Slew rate ≥ 1V/μs

- Phase margin ≥ 45°

- $\rightarrow$  Matlab design matches simulated circuit within 10% except for  $f_T$

- Design point corresponds to both stages operating in moderate inversion with  $(I_D/I_S)_1 = 2.9$  and  $(I_D/I_S)_2 = 6$

#### **SPICE** optimization

## **Conclusion**

- Design model based on charge-sheet is proposed\*

- > Good match with measurement with just a few parameters

- > MOSFET models for design differ from simulation ones

- Need to be simple enough but accurate

- Describe operation in all regions of operation

- Contain very few parameters

- Closer to physics

- - Automated design flow

- > Opamp synthesis using simple model is verified and improved by complete simulation

<sup>\*</sup> P. G. A. Jespers, "The gm/ID Methodology, a Synthesis Tool for Low-Voltage Analog CMOS Circuits, Springer, to be published spring 2007