# A New Spice Model for CNTFET Based on the Nano-model

Institute of Microelectronics of Chinese Academy of Sciences, IMECAS

Fu Bo

1. Introduction

- **2.** Model Optimization

- 3. Model Verification

1

## Introduction

#### Comparison between CNT and Si

|     | Bandgap<br>(eV) | Electron<br>mobility<br>(cm²/V·s) | Saturated<br>electron<br>velocity<br>(×10 <sup>7</sup> cm/s) | Thermal<br>conductivity<br>(W/cm·K) |

|-----|-----------------|-----------------------------------|--------------------------------------------------------------|-------------------------------------|

| CNT | ~0.9            | 100000                            | 4                                                            | >30                                 |

| Si  | 1.1             | 1500                              | 1                                                            | 1.5                                 |

A promising material for the more Moore solutions——CNT

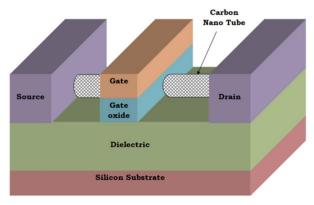

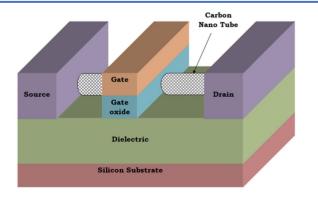

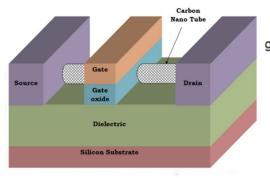

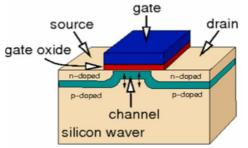

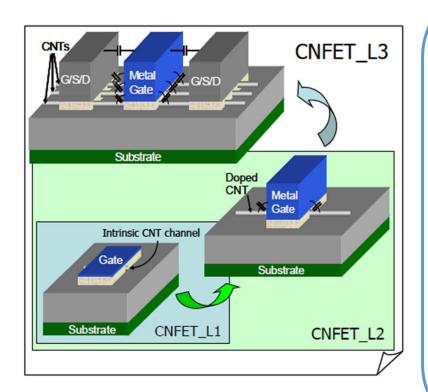

This is the schematic view of the CNTFET

The unique electron transport properties and band structure of nanotubes, and their quasi 1-D geometries make semiconducting SWNTs ideal channel materials for high-speed and low-power electronics.

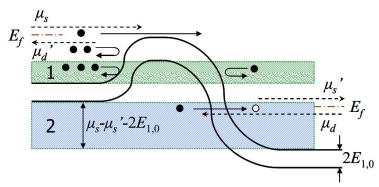

This is the schematic view of the energy band of MOS-like

Due to the different work functions of the doped source/drain of CNTFET and undoped CNT, the energy band will be bent, so there will be a potential barrier in the channel to block the carrier transmission. By changing the gate voltage, the barrier height can be adjusted, so that the current can be controlled.

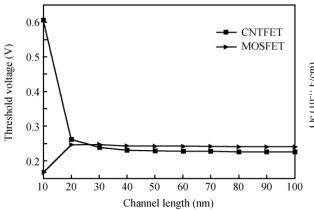

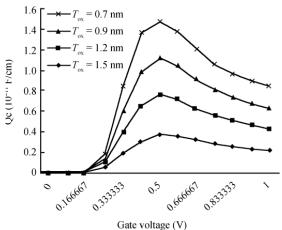

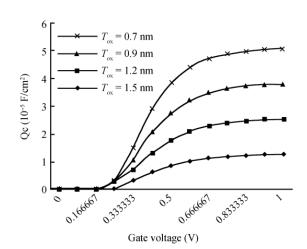

- Threshold Voltage

- Quantum Capacitance

#### **CNTFET**

#### **MOSFET**

Numerical Model: FETToy ...

Analytical Model: ROY Stanford Nano Model ...

Semi-empirical Model: Virtual Source Model ...

[1]A. Rahman, Jing Guo, S. Datta and M. S. Lundstrom, "Theory of ballistic nanotransistors," in IEEE Transactions on Electron Devices, vol. 50, no. 9, pp. 1853-1864, Sept. 2003, doi: 10.1109/TED.2003.815366.

[2]A. Raychowdhury, S. Mukhopadhyay, K. Roy, A circuit-compatible model of ballistic carbon nanotube field-effect transistors. IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS 23, 1411-1420 (2004)

[3]A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application - Part I: Model of the intrinsic channel region. IEEE TRANSACTIONS ON ELECTRON DEVICES 54, 3186-3194 (2007).

[4]J.Deng, H.S.P.Wong, A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application - Part II: Full device model and circuit performance benchmarking. IEEE TRANSACTIONS ON ELECTRON DEVICES 54, 3195-3205 (2007)

[5]C. S. Lee, E. Pop, A. D. Franklin, W. Haensch, H. S. P. Wong, A Compact Virtual-Source Model for Carbon Nanotube FETs in the Sub-10-nm Regime-Part I: Intrinsic Elements. IEEE TRANSACTIONS ON ELECTRON DEVICES 62, 3061-3069 (2015)

[6]C.S.Lee, E.Pop, A.D.Franklin, W.Haensch, H.S.P.Wong, A Compact Virtual-Source Model for Carbon Nanotube FETs in the Sub-10-nm Regime-Part II: Extrinsic Elements, Performance Assessment, and Design Optimization. IEEE TRANSACTIONS ON ELECTRON DEVICES 62, 3070-3078 (2015)

**1st Level:** Intrinsic channel region with nearballistic transport, and without any parasitic capacitance and parasitic resistance.

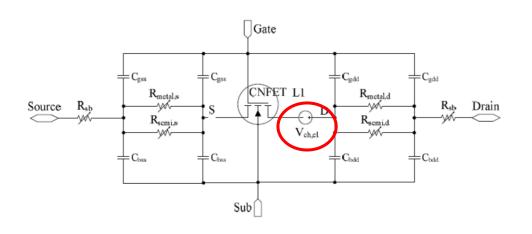

2nd Level: The practical device non-idealities, including the elastic scattering in the channel region, the quantum/series resistance and the parasitic capacitance of the doped source/drain region, and the Schottky barrier (SB) resistance.

**3rd Level:** The top of the model, which allows for multiple CNTs for each device, and the CNTs are grouped into the CNTs at the two edges and CNTs in the middle.

2

# Model Optimization

- Substrate bias effects

- Transmission probability

- SS Factor

- **BTBT** current

## >>> Substrate bias effects

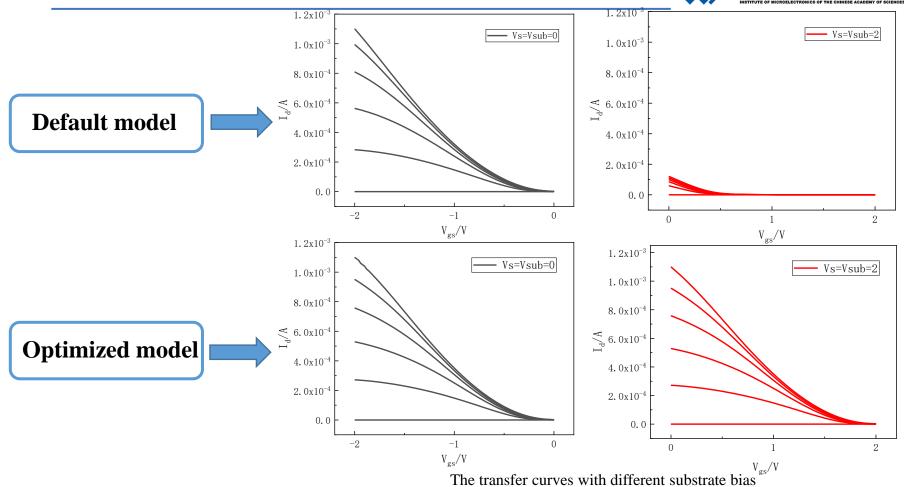

In the Stanford nano-model, port voltages are all absolute voltages, which leads to errors in the voltages input to the model, causing incorrect results. Consequently, substrate bias effects can not be implemented correctly in the Verilog-a model.

Subtracting a reference voltage from the port voltage input to the model

## >>> Substrate bias effects

- Substrate bias effects

- Transmission probability

- SS Factor

- BTBT current

**Non-ballistic transport:** For real devices with >100 nm channel length, nonballistic transport cannot be excluded. In this case, transmission probability is not 1. Besides, transmission probability can be affected by the optical phonon scattering and acoustic phonon scattering.

The effective mean free path of optical phonon scattering in the ballistic transport model is as follows:

$$l_{op}(V_{xs}, m, l) = \frac{\lambda_{op}D_o}{D(E_{m,l} - \hbar\Omega)[1 - f_{FD}(E_{m,l} - \hbar\Omega - \Delta\Phi_B + eV_{xs})]}$$

The transmission probability is:

$$T_{LR} = \frac{l_{eff}(V_{ch,DS}, m, l)}{l_{eff}(V_{ch,DS}, m, l) + L_g} \qquad T_{RL} = \frac{l_{eff}(0, m, l)}{l_{eff}(0, m, l) + L_g}$$

$T_{LR}$  and  $T_{RL}$  are the transmission probability of the carriers at the sub-state (m,l) in +k branch and –k branch, respectively.

The wave numbers related with semiconducting subbands are given by:

$$k_m = \frac{2\pi}{a\sqrt{n_1^2 + n_1 n_2 + n_2^2}} \cdot \lambda$$

$$\lambda = \begin{cases} \frac{6m - 3 - (-1)^m}{12} & m = 1, 2, \dots, mod(n_1 - n_2) \neq 0 \\ m = 0, 1, \dots, mod(n_1 - n_2) = 0 \end{cases}$$

$$k_l = \frac{2\pi}{L_a}l$$

$l = 0,1,2,...$

CNT E-k dispersion relation can be approximated as:

$$E_{m,l} \approx \frac{\sqrt{3}}{2} \alpha V_{\pi} \sqrt{k_m^2 + k_l^2}$$

Em,l is the carrier energy at the (m,l) sub-state above the intrinsic level Ei

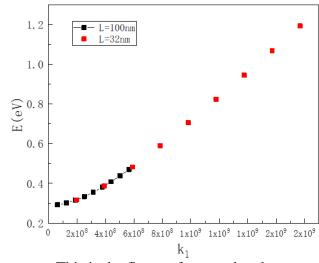

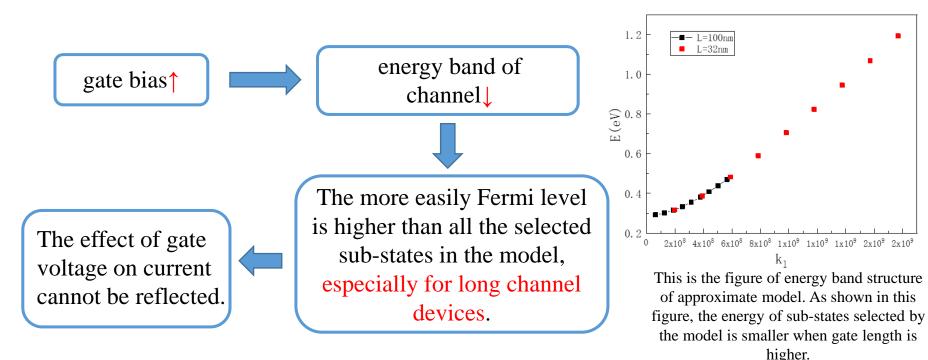

This is the figure of energy band structure of approximate model. As shown in this figure, the energy of sub-states selected by the model is smaller when gate length is 100nm.

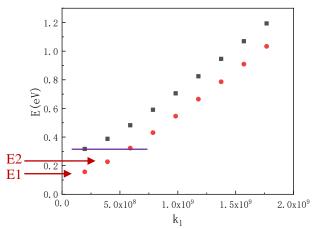

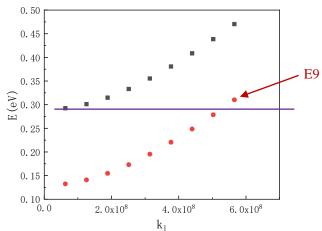

The energy of the sub-states selected by the model (black square), and the energy of the substate after subtracting the energy  $\hbar\omega$  (~ 0.16 eV) required for optical phonon scattering (red dot). (a) The channel length is 32nm (b) The channel length is 100nm

#### **Conditions of scattering:**

- (1) the sub-state  $(m,l_1)$  is filled with electrons.

- (2) the sub-state  $(m,l_2)$  is empty so it can accept the scattered carrier from  $(m,l_1)$ .

Then the model is optimized, the Fermi-Dirac distribution function of the source and drain and the transmission probability of the source and drain carriers need to be related to the gate voltage. The mobility model in the BSIM model is used as a reference:

$$\mu_{eff} = \frac{\mu_o}{1 + \left(U_a + U_c V_{bseff}\right) \left(\frac{V_{gsteff} + 2V_{th}}{T_{ox}}\right) + U_b \left(\frac{V_{gsteff} + 2V_{th}}{T_{ox}}\right)^2}$$

Three parameters are added to make the current transmission probability and Fermi-Dirac distribution function depend on the gate voltage.

$$tempTT = \frac{coeffvg0}{1 + coeffvg1*(v\_vg - v\_vs) + coeffvg2*(v\_vg - v\_vs)*(v\_vg - v\_vs))}$$

- Substrate bias effects

- Transmission probability

- SS Factor

- **BTBT** current

The formula for calculating SS is:

$$S = n \left(\frac{kT}{q}\right) ln(10)$$

For the ideal transistor subthreshold coefficient n=1, for the actual device, n depends on the device itself.

In Stanford Nano-model, however, there are no parameters in the model which can directly adjust the subthreshold slope.

To solve the problem mentioned above, parameter *n* was added to the model.

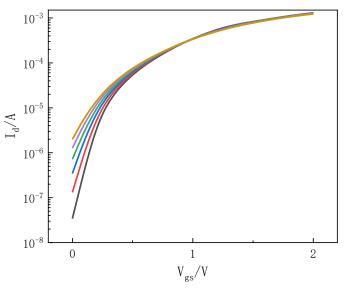

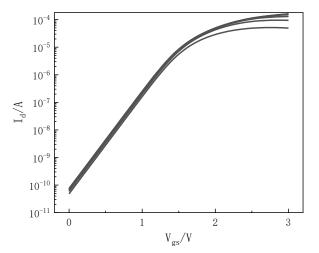

Transfer characteristic curve with different coefficients after adding subthreshold coefficient.

- Substrate bias effects

- Transmission probability

- SS Factor

- **BTBT** current

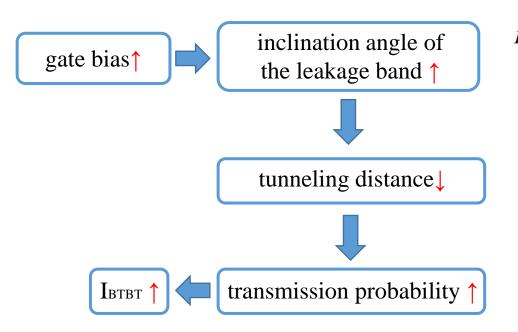

**Band-to-band tunneling effect** :electrons from valence band can tunnel to conduction band under low voltage or negative voltage, which contributes to the total current of transistor and leads to the increase of current under negative voltage.

BTBT only occurs at the drain junction and only if the following two conditions are met:

- (1) the conduction band at the drain side is below the valence band at the source side and

- (2) there are empty states at the drain side to accept the tunneling carriers.

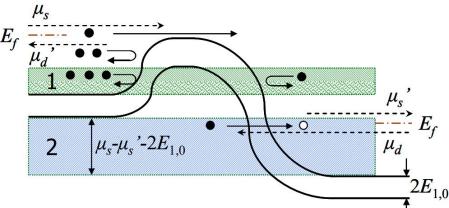

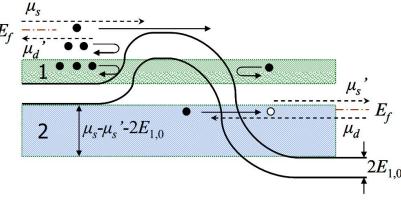

There are two possible tunneling regions: the "n" shape region 1 and the "L" shape region 2. Because the tunneling through the source junction in region 1 is prohibited, we only consider the BTBT current through the drain junction in region 2.

IBTBT is the leakage current between drain and source due to band-to-band (BTBT) tunneling effect.

There are two possible tunneling regions: the "n" shape region 1 and the "L" shape region 2. Because the tunneling through the source junction in region 1 is prohibited, we only consider the BTBT current through the drain junction in region 2.

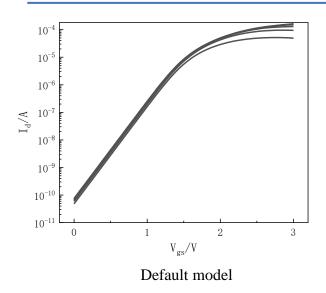

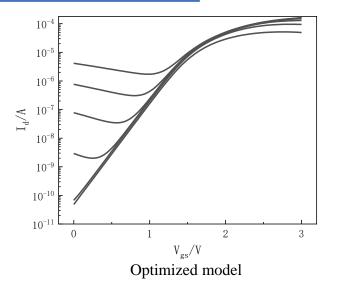

Transfer characteristic curve with BTBT current model before optimization

The second-level equivalent circuit model of CNTFET

Since the leakage voltage transmitted from the Level 2 of the nano model into the Level 1 will be greatly reduced due to the partial pressure of the considered nonideal factors, the  $V_{DS}$  input into the Level 1 is too small to meet the conditions for the occurrence of the band-to-band tunneling current.

For practical devices, the non-ideal factors of the channel region will not affect the applied voltage difference between the source and drain terminals. Therefore, it is considered to change the internal source drain voltage in the BTBT current model to the external source drain voltage.

3

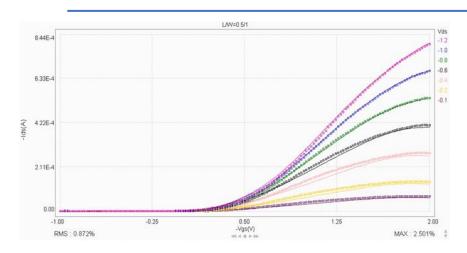

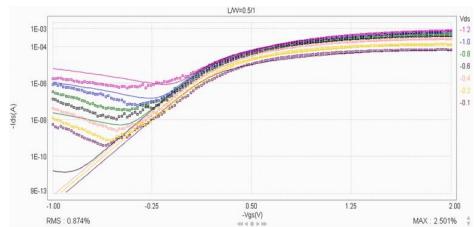

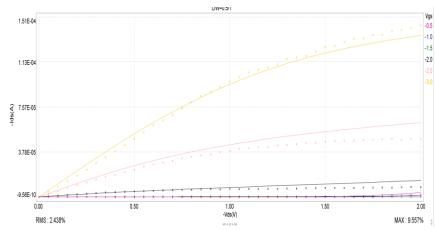

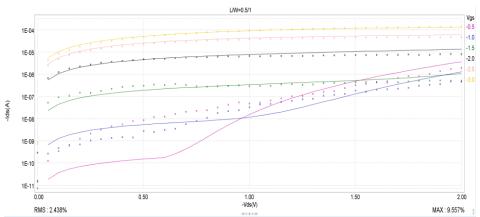

## Model Verification

#### >>> Model Verification

#### >>> Conclusion

Substrate bias effects: By Subtracting a reference voltage from the port voltage input to the model, substrate bias effects can be implemented correctly in Verilog-A model.

Transmission probability: The influence of gate voltage is introduced into the transmission probability calculation formula.

SS Factor: By introducing the subthreshold coefficient N, this model can fit practical devices more easily.

BTBT current: The calculation method of tunneling voltage in the model is improved.

# Thanks