#### The Robuspic Project – An Overview

Christian Maier, Robert Bosch GmbH - on behalf of all partners -

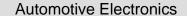

#### **Automotive Electronics**

### The Robuspic Project –An Overview

- → Motivation

- Organization

- → Work Packages

- → Results

- → Conclusion

#### **Robuspic - Motivation**

#### **Smart Power circuits...**

- ... typically combine:

- Highly accurate analog circuitry

- Digital signal processing

- Driving heavy loads

- ... operate in an uncontrolled environment

- Extended Temp. range

- E-M disturbances

- ... should have good, predictable reliability in harsh environment

... should have competitive cost

#### **Robuspic: Organization**

#### **ROBUSPIC:**

Robust Mixed Signal Design Methodologies for Smart Power ICs

- → An Information Society Technologies Project Funded by the European Commission in Framework 6

- → Duration: December 2003 until November 2006

#### **Robuspic - Organization**

#### Partners:

- AMI Semiconductor (Belgium, Project Leader)

- Cadence (France)

- Cambridge Semiconductors (UK)

- EPFL (Switzerland)

- University of Cambridge (UK)

- IMEC (Belgium)

- KU Leuven (Belgium)

- University of Zagreb (Croatia)

- Robert Bosch GmbH (Germany)

#### **ROBUSPIC - Work Packages**

- → WP1: Compact Models

- Development of L- and VDMOS models based on the EKV approach for the channel region

- Development of LIGBT models

- → WP2: Reliability

- Investigation of degradation mechanisms at DMOS and LIGBTs

2. Aging

- Development of aging models

- WP3: Sensitivity Modeling

- Model extensions for matching, process and layout sensitivities

- → WP4: System Level Aspects

- Methods for fast simulation on system level

- Electro thermal simulation

- Simulation of EMC

- WP5: Validation

- Assessment of gain in simulation accuracy & speed

1. Models **DMOS LIGBT** 3. Sensitivity 5. Validation **Impementation** 4. System **EMC Thermal**

#### **Automotive Electronics**

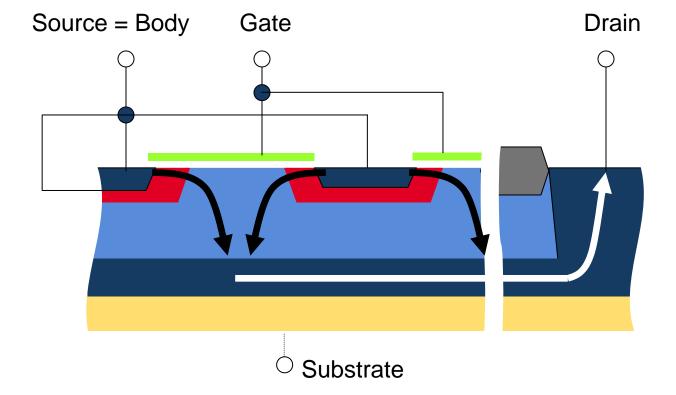

## **VDMOS Transistor - Schematic Cross Section**

# **LDMOS Transistor - Schematic Cross Section** Source = Body Drain Gate Substrate 8

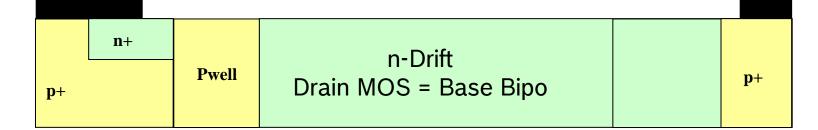

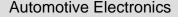

#### **LIGBT - Schematic Cross Section**

Cathode Anode

#### Work Package 1

# **DMOS Model Approach**

- Base: EKV V2.6 for Channel Region Modeling

- > Drift Region modeled by voltage dependent resistor

- Correct modeling of « quasi-saturation »

- > EKV formulation modified for charge calculation

- > Correct modeling of bias-dependent capacitances

- Self heating effects included

- ➤ Different geometry scaling for L- and VDMOS devices

#### **Work Package 1**

# **DMOS Model Approach**

- > 8 EKV model parameters (channel region)

- ➤ 12 Drift region parameters (R<sub>D</sub>, C<sub>GD</sub>)

- ➤ 4 thermal parameters

- > 3 self heating parameters

- ➤ 4 impact ionisation parameters

- > 8 (+x) parameters for parasitics

#### **Work Package 1: Modeling**

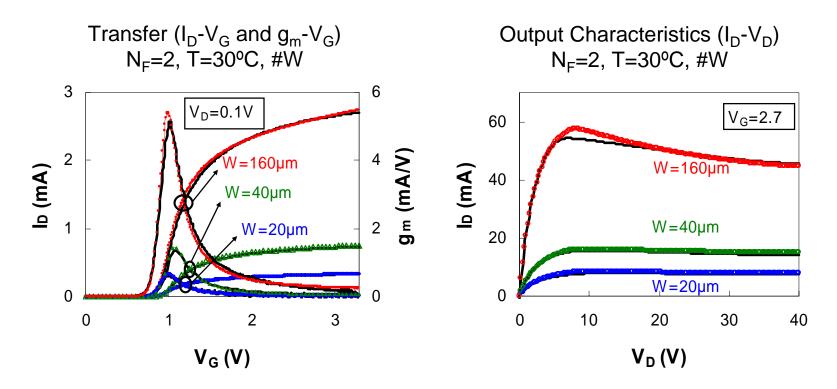

➤ Correct W scaling for transfer and output characteristics, including g<sub>m max</sub> and Self Heating

#### **Work Package 1: Modeling**

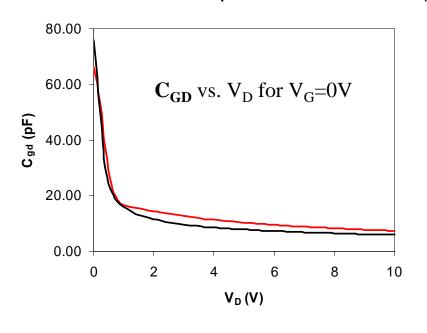

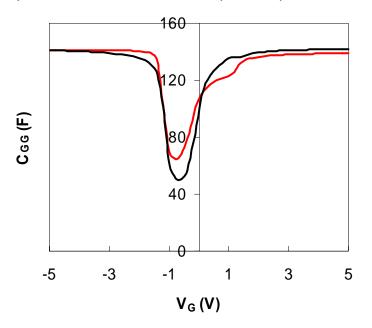

#### LDMOS Capacitances: Model (red) vs Measurement (black)

#### **Automotive Electronics**

#### **Work Package 1: Modeling**

#### LIGBT Model

- Based on Hefner model for vertical IGBTs

- Modifications for lateral IGBTs to account for differences in

- Carrier dynamics

- Terminal capacitances

- Substrate effects

- Parasitic effects (resistor, JFET)

- → Development by use of TCAD simulations & measurements at devices fabricated at CamSemi (SOI & junction isolated)

- Implementation in Pspice and Verilog-A

## **LIGBT - Equivalent Circuit**

15

disposal such as copying and passing on to third parties.

AE/EIM1-Heinisch | 30/01/2006 | © Robert Bosch GmbH reserves all rights even in the event of industrial property rights. We reserve all rights of

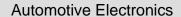

#### **Work Package 2: Reliability**

- Investigations of devices under static and dynamic stress conditions

- Temperature range -40 to 200°C

- Consideration of process deviations

- Identification of main stress mechanisms, also by use of TCAD

- Development of degradation models for DMOS and LIGBT device parameters (HCI)

- Implementation into the circuit models developed in WP1

- Development of supplementary circuits for life condition monitoring

## Work Package 3: Layout & Process Sensitivities

- Topics addressed in this work package:

- Investigation of process parameter variations on on-state performance

extension to statistical model

- Matching (Mismatch models for L- and VDMOS)

- Scaling: Investigation of several scaling options (e.g. fingers or cells) for both DMOS and LIGBT

#### **Work Package 4: System Level Aspects**

- Investigation of Methods to speed up simulation of smart power circuits

- Automatically generated "Black Box Models" for circuit blocks

- Transistor Level Simulation using Fast Spice Simulators

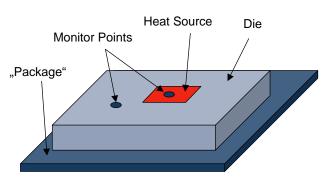

- Development of Methods for Electro-Thermal Simulation

- Package modeling

- Scalable thermal impedances of power devices

- Coupled electro thermal simulation

- Development of models and methods for EMC simulation

UNIVERSITYOF CAMBRIDGE

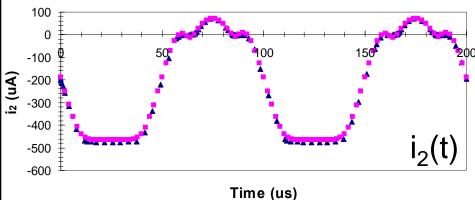

#### **Work Package 4: System Level Aspects**

f=10KHz,

$$V_{ac}$$

=1.0 V,  $V_{dc}$ =1.0V

R<sub>F</sub>=100Ω, R<sub>I</sub>=1300Ω

1.6

1.4

1.2

1.0.8

0.6

0.4

0.2

100

Time (us)

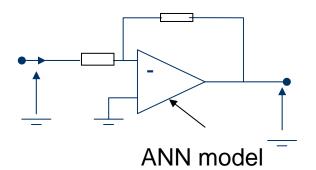

"Black Box" Model Approach: Model Generation by training of artificial neural networks

Output from ANN model (\*) Output from compact model (

200

150

**Automotive Electronics**

50

0

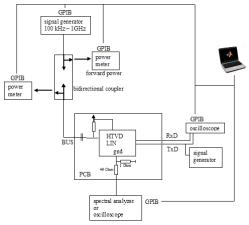

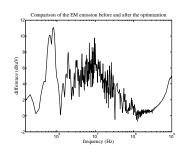

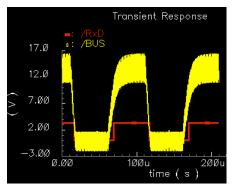

#### **Work Package 4: IC Level EMC**

## IC level EMC

EME and EMI HTVD measurement system

EMC aware circuit optimizations

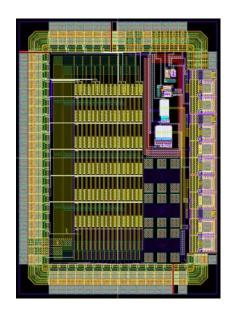

EMC test chip

Interface for EMC simulations in Cadence environment

#### **Work Package 4: System Level Aspects**

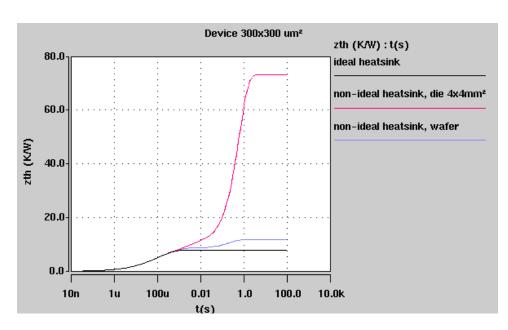

#### Derivation of Scalable Model for Thermal Device Impedance

Thermal simulation Setup

Thermal Simulation Result: Thermal Impedance vs time for 3 device mounting conditions

#### **Work Package 5: Validation**

- Implementation of DMOS and LIGBT models into design environments

- Selection of demonstrator circuits

- Implementation of methods into the industrial design flows

- Assessment of new models and methods regarding accuracy and performance

# **Work Package 5: Validation DMOS** model implementation Direct transfer **AHDLCMI** Verilog-A Simulator: Spectre/UltraSim AMIS/Cadence Verilog-A Simulator: Eldo **EPFL** C-Core Translation MAST-Shell Simulator: Saber Bosch **Automotive Electronics** AE/EIM1-Mc | 30/01/2006 | © Robert Bosch GmbH reserves all rights even in the event of industrial property rights. We reserve all rights of 24 disposal such as copying and passing on to third parties.

#### **Robuspic - Highlights**

- → Scalable models for LDMOS, VDMOS, SOI LIGBT available

- Self heating effect included

- Extension with parasitic bipolars implemented

- → DMOS Degradation investigated, analytical aging formulation and parameter degradation models available

#### **Work Package 6: Dissemination**

#### **Robuspic Workshops:**

June 2005 at ISIE Dubrovnik

Planned: June 4th, 2006 at ISPSD Naples

Planned: September 22<sup>nd</sup>, 2006 at ESSDERC Montreux

**Robuspic Website:**

http://www-g.eng.cam.ac.uk/robuspic/