# Thermal Network Extraction in Ultra-Thin-Body SOI MOSFETs

Y. S. Chauhan<sup>1,2</sup>, M. A. Karim<sup>2</sup>, A. M. Niknejad<sup>2</sup> and C. C. Hu<sup>2</sup>

<sup>1</sup>Indian Institute of Technology (IIT)

Kanpur, India

<sup>2</sup>University of California Berkeley, USA

## Outline

• Introduction

• Thermal Network Characterization

Results

Other News

## Introduction

• Carrier scattering leads to heat generation

• Dominant at drain end of MOSFET due to high field

• Temperature increase affects device parameters e.g. threshold voltage, mobility etc.

3

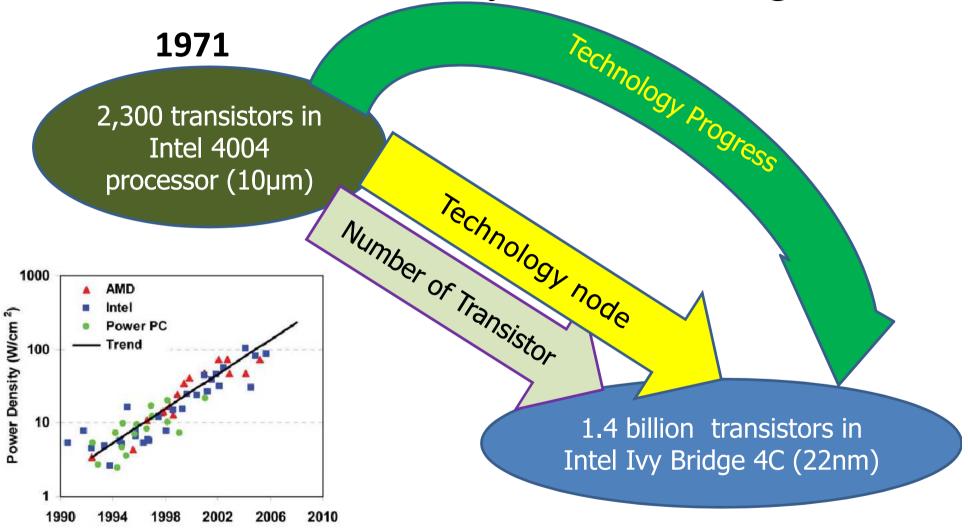

# Power Density and scaling

Figure: Trend of on chip power density over the past 10 years. Solid line marks an exponential trend.

Source: E. Pop et al., "Heat Generation and Transport in Nanometer-Scale Transistors". Proceedings of the IEEE , August 2006.

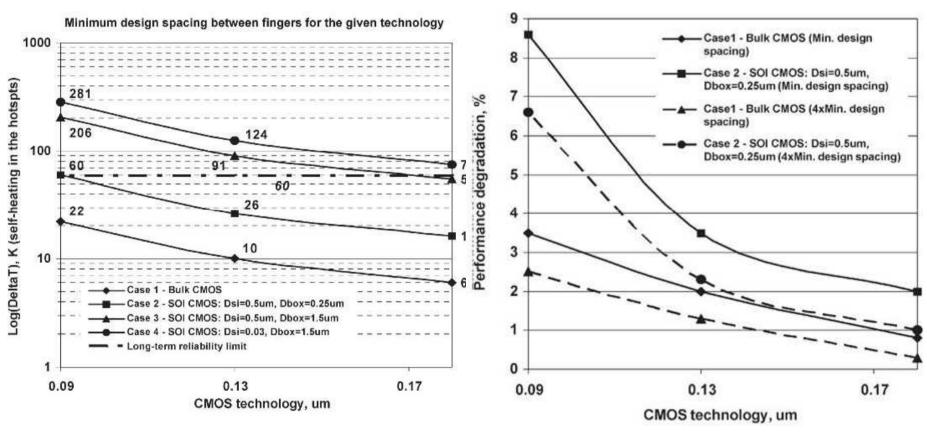

# Self Heating & Technology Scaling

Figure: Increase in  $\Delta T$  with technology scaling

Figure: Performance degradation of a three stage ring oscillator due to self heating effect versus technology scaling

## Self Heating: Effect of Structure/Technology

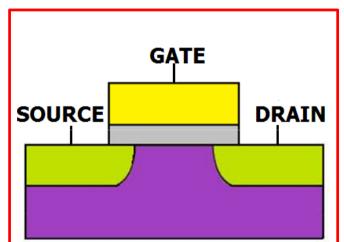

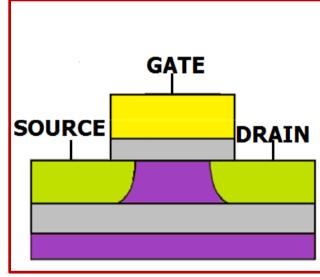

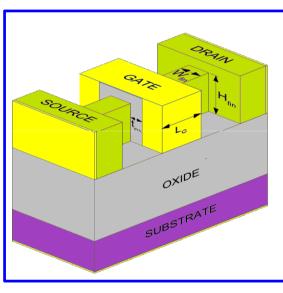

#### **Evolution of MOSFET Architecture**

#### **Bulk MOSFET**

#### **SOI MOSFET**

#### **FinFET**

6

- Technology scaling achieved by

- New materials (SOI, High-K dielectric, Strained Silicon etc.)

- Highly confined geometry

- New materials and greater confinement increased self heating effect

Yogesh S. Chauhan

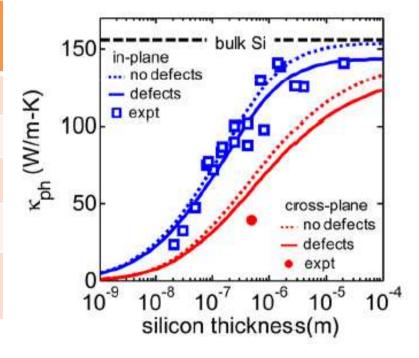

# Confinement & Thermal Conductivity

- Bulk Si 50% of the heat conduction is carried by phonons with a mean-free-path greater than about 1  $\mu m$ .

- For film thickness is smaller than  $\sim 200nm$ , 50% of the heat is carried by phonons with mean-free-paths longer than the film thickness.

| Material                  | Thermal conductivity (W/m-K) |

|---------------------------|------------------------------|

| Si(Bulk)                  | 149                          |

| Ge                        | 60.2                         |

| SiO <sub>2</sub>          | 1.4                          |

| HfO <sub>2</sub> (>500nm) | 1.2                          |

| HfO <sub>2</sub> (3nm)    | 0.27-0.49                    |

Source: Ch. Jeong, S. Datta, M. Lundstrom "Thermal conductivity of bulk and thin-film silicon: A Landauer approach" JOURNAL OF APPLIED PHYSICS 111, 093708 (2012)

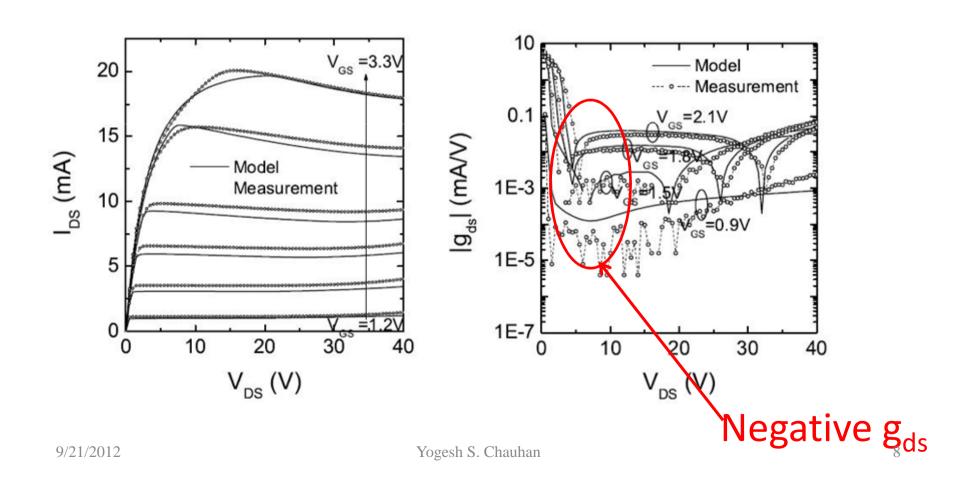

# Impact of Self Heating

#### Note decrease in current with VDS

# Self Heating Measurement

- Gate Current measurement

- Requires dedicated structures

- Measures gate temperature

Ref.: S. Khandelwal et al., "Scalable Thermal Resistance Model for single and multi-finger Silicon-on-Insulator MOSFETs", IEEE ICMTS, April 2011

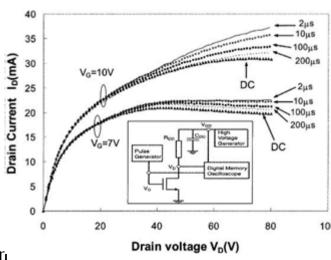

## • Pulsed measurement technique

- DC structures can be used

- Requires dedicated setup

- Works upto limited frequencies.

Ref.: C. Anghel et al., "Self-heating characterization and extraction method for thermal resistance and capacitance in HV MOSFETS", IEEE EDL 2004

Yogesh S. Chauhan

Figure: Output characteristics of n-channel DMOSFET. Comparison b/w steady state DC measurement and different pulse width measurement. Inset the measurement setup.

# Self Heating Measurement

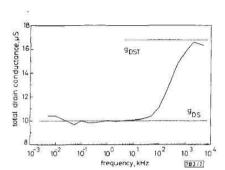

- Small signal conductance technique

- DC structures can be used

- Widely used technique

Fig. 2 Measured drain conductance against frequency for 20  $\mu$ m wide 3  $\mu$ m partially depleted SIMOX MOSFET with source connected body tie [8]

- What if there is no clear self heating free region?

Ref.: W. Redman-White et al., "Direct Extraction of MOSFET Dynamic Thermal Characteristics from Standard Transistor Structures using Small Signal Measurements", Electronics Letters, June 1993.

Ref.: Wei Jint et al., "Self-Heating Characterization for SOI MOSFET Based on AC Output Conductance", IEDM 1999

- S- parameter measurement technique

- Versatile technique

- Requires dedicated RF structures and measurements

Ref. 1: M. A. Karim et al., "Extraction of Isothermal Condition and Thermal Network in UTBB SOI MOSFETs", IEEE EDL 2012

Ref. 1: A.J. Scholten et al., "Experimental assessment of self-heating in SOI FinFETs", IEDM 2009

Ref. 2: N. Rinaldi et al., "Small-Signal Operation of Semiconductor Devices including Self-heating, with Application to Thermal

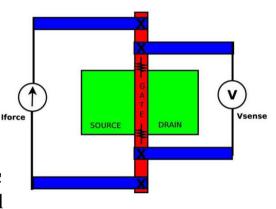

## S-parameter measurement

• S-parameters measured using vector network analyzer (VNA) (e.g. Agilent E5071C ENA with frequency range of 100 kHz–8.5 GHz)

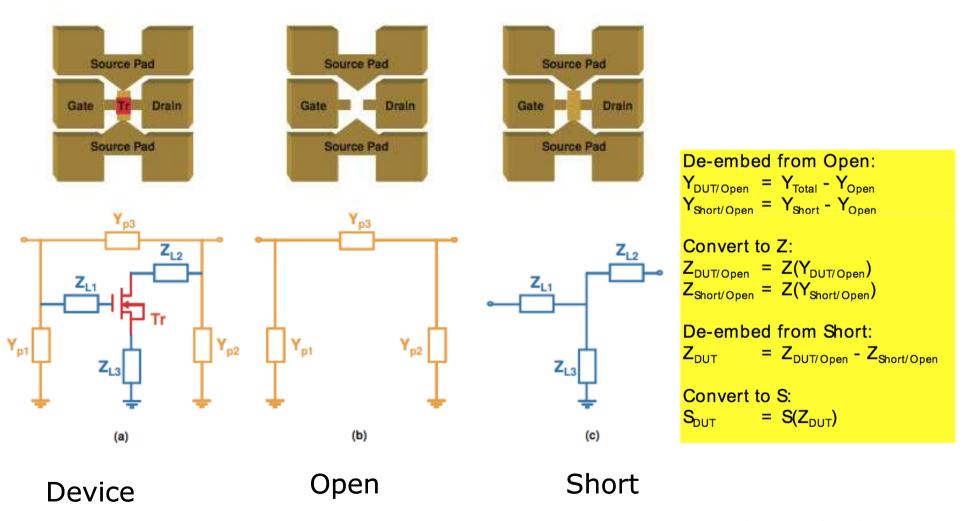

### De-embedding

- Use de-embedding to remove parasitics

- Probe/wire parasitics are de-embedded using calibration substrate

- Pads to device parasitics are de-embedded using OPEN-SHORT de-embedding

## Self Heating: Open-Short De-embedding

Yogesh S. Chauhan

Courtesy: Agilent Technologies

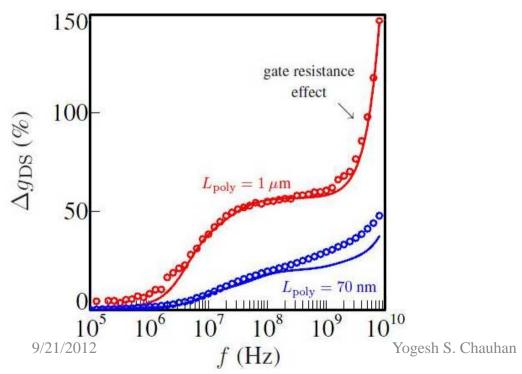

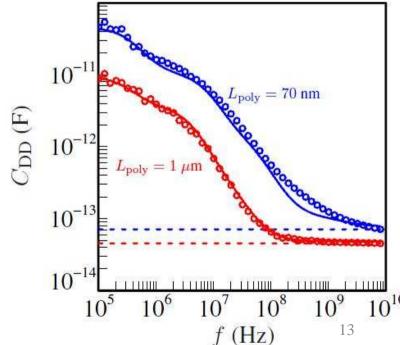

### Issues in thermal network extraction

• No self heating free region in gds due to parasitics in short channel devices

• Electrical contribution in C<sub>DD</sub> cannot explain 2-3

order decrease

Ref.: A.J. Scholten et al., "Experimental assessment of self-heating in SOI FinFETs", IEDM 2009

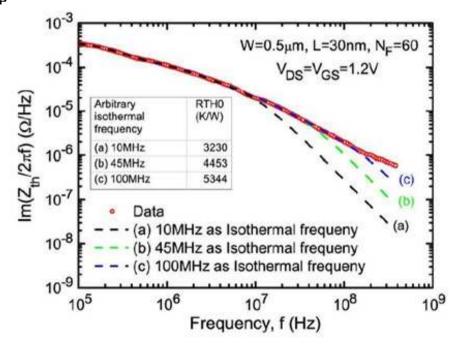

## Issues in thermal network extraction

Impact of choosing arbitrary isothermal frequency

Figure: Extraction of DC thermal resistance (RTH0) using different arbitrary isothermal frequencies.

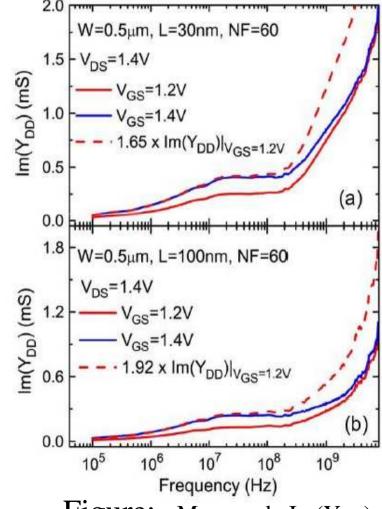

# Our Approach: Thermal Network Extraction

- Thermal contribution in Im(Y<sub>DD</sub>) dominates over electrical (substrate and/or gate resistance network) at lowfrequency

- Im(Y\_DD) at  $V_{GS}$ =1.4V  $\propto$  Im(Y\_DD) at  $V_{GS}$ =1.2V

- Proportionality constant depends on the ratio of currents

- Around isothermal frequency, electrical contribution start dominating over thermal contribution to  $Im(Y_{DD})$ , and proportionality relationship becomes invalid

- Frequency at which splitting happens is the isothermal frequency

Figure: Measured Im(Y<sub>DD</sub>) of UTBSOI MOSFET 15

# Our Approach: Thermal Network Extraction

• Simultaneous fitting of  $Re(Y_{DD})$  and  $Im(Y_{DD})$  as both are sensitive to change in temperature.

$$Z_{\text{th}} = \frac{Y_{\text{DD}} - Y_{\text{DD}}^{\text{iso}}}{\frac{dI_{\text{DS}}}{dT_{\text{abm}}} (I_{\text{DS}} + V_{\text{DS}}.Y_{\text{DD}})}$$

$$Im(Y_{DD}) = \frac{Im(Z_{th}) \left[ Re(Dn)^2 + Im(Dn)^2 \right]}{Re(Dn)} + \frac{\left[ Re(Y_{DD}) - (Y_{DD}^{iso}) \right] Im(Dn)}{Re(Dn)}$$

Where,

$$D_{n} = \frac{dI_{\rm DS}}{dT_{\rm amb}} \left(I_{\rm DS} + V_{\rm DS}.Y_{\rm DD}\right)$$

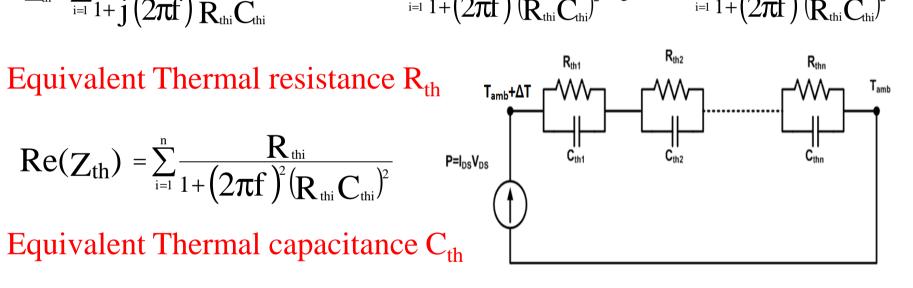

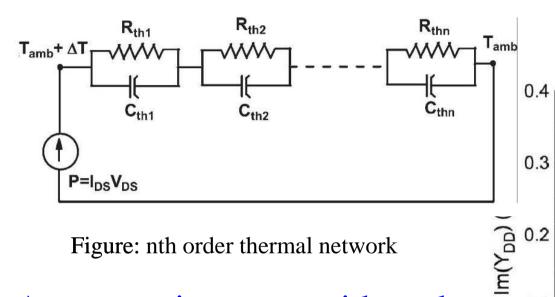

# Self Heating: Thermal network

## Thermal impedance of n<sup>th</sup> order thermal N/W

$$Z_{\rm th} = \sum_{\rm i=1}^{\rm n} \frac{R_{\rm thi}}{1 + j \left(2\pi f\right) R_{\rm thi} C_{\rm thi}} \qquad \text{or} \qquad Z_{\rm th} = \sum_{\rm i=1}^{\rm n} \frac{R_{\rm thi}}{1 + \left(2\pi f\right)^2 \left(R_{\rm thi} C_{\rm thi}\right)^2} - j \left(2\pi f\right) \sum_{\rm i=1}^{\rm n} \frac{R_{\rm thi}^2 C_{\rm thi}}{1 + \left(2\pi f\right)^2 \left(R_{\rm thi} C_{\rm thi}\right)^2}$$

$$Re(Z_{th}) = \sum_{i=1}^{n} \frac{R_{thi}}{1 + (2\pi f)^{2} (R_{thi} C_{thi})^{2}}$$

Figure: nth order thermal network

$$\lim_{t \to \infty} (Z_{th})^{2\pi f} = \sum_{i=1}^{n} \frac{R_{thi}^{2} C_{thi}}{1 + (2\pi f)^{2} (R_{thi} C_{thi})^{2}} \quad DC \text{ Thermal resistance RTHO}$$

RTH0 =

$$R_{th}|_{f=0} = \sum_{i=1}^{n} R_{thi}$$

## Order of thermal network

Figure: nth order thermal network

Accuracy increase with order of network but computational efficiency of the model goes down

$10^{6}$ 10<sup>5</sup> Frequency (Hz) Figure: Fitting of Im(Y<sub>DD</sub>) using various-order thermal networks independently. Results are shown for the self-heating dominated segment of the

W=1µm, L=30nm, NF=30

RTH0

(K/mW)

2.987

3.273 3.285

> 2<sup>nd</sup>order thermal network 3<sup>rd</sup> order thermal network

th order thermal network

$V_{DS} = V_{CS} = 1.2V$

Network

Order

0.1

0.0

## Results

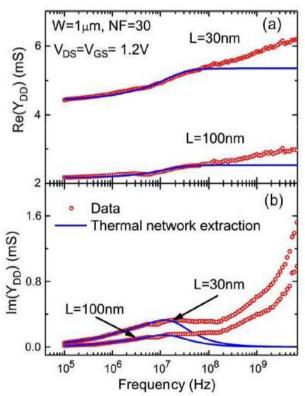

• Third order network extracted by simultaneous fitting of  $Re(Y_{DD})$  and  $Im(Y_{DD})$

Figure: Measured and extracted Re( $Y_{DD}$ ) and  $100 \text{ Im}(Y_{DD})$  on 30nm and 100nm length effe UTBSOI devices.  $V_{GS} = V_{DS} = 1.2 \text{V}$ .

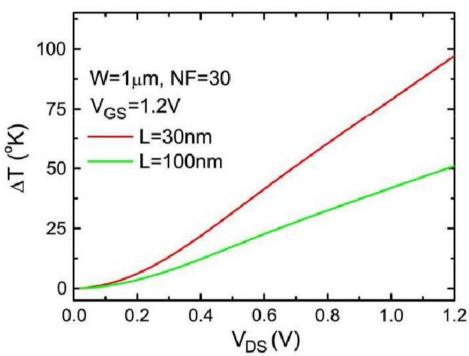

Figure: DC temperature rise for 30nm and 100nm length devices due to self heating effect.

## Self Heating – Should we care?

- Digital circuits operate in 1-2 GHz range

- No effect of self heating ©

- RF circuits operate in 5-100 GHz range

- No effect of self heating ☺

- Analog circuits operate in KHz-MHz range

- Self heating is dominant up to ~30-40 MHz

- Analog designers should be careful

## Conclusion

- A better approach for thermal network extraction was presented

- Temperature may rise by more than 100°C due to self heating effect in SOI devices

- I<sub>dsat</sub> decreases around 4-5%

- Digital and RF circuits doesn't get affected by SHE

- Analog circuits do have performance degradation

- Ref.

- M. A. Karim, Y. S. Chauhan, S. Venugopalan, A. B. Sachid, D. D. Lu, B. Y. Nguyen, O. Faynot, A. M. Niknejad, and C. Hu, "Extraction of Isothermal Condition and Thermal Network in UTBB SOI MOSFETs", IEEE Electron Device Letters, Vol33, No.9, Sept. 2012.

## Other News

- Released BSIM6.0.0-beta8 in Aug. 2012 with improved global scaling

- Received Excellent feedback on the model

- Released CMC standard BSIM-CMG 106.1.0 in Sept. 2012

- Released BSIM4.7.1-beta for testing

- Released BSIMSOI4.5-beta for testing

# Acknowledgment

- Chandan Yadav (IIT Kanpur)

- Sourabh Khandelwal (NTNU, Norway)

- Bich-Yen (SOITEC, USA)

- Olivier Faynot (LETI, Grenoble)

- Darsen Lu (IBM, Fishkill)

- Maryam (Sahar) Tabesh (UCB)

- Cristian Marcu (UCB)

- Amin Arbabian (UCB)